**User's Manual**

# **78K/IV Series**

# **16-Bit Single-Chip Microcontroller**

Instructions

For All 78K/IV Series

Document No. U10905EJ8V1UM00 (8th edition) Date Published March 2001 N CP(K)

© NEC Corporation 1997 Printed in Japan [MEMO]

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to V<sub>DD</sub> or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

IEBus and QTOP are trademarks of NEC Corporation.

MS-DOS and Windows are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

Ethernet is a trademark of Xerox Corporation.

TRON is an abbreviation of The Realtime Operating System Nucleus.

ITRON is an abbreviation of Industrial TRON.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

Caution: Purchase of NEC I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

- The information in this document is current as of January, 2001. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC semiconductor products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades: "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

(1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

# Major Revisions in This Edition

| Pages      | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout | <ul> <li>Addition of μPD784216A, 784216AY, 784218A, 784218AY, 784938A, 784956A, 784976A Subseries.<br/>Deletion of μPD784216, 784216Y, 784218, 784218Y, 784937, 784955 Subseries.<br/>Addition of μPD784928, 784928Y. Deletion of μPD784915, 784915A, 784916A</li> <li>The status of following products changed from under development to completed:<br/>μPD784224, 784225, 78F4225, 784224Y, 784225Y, 78F4225Y</li> <li>μPD784907, 784908, 78P4908</li> </ul> |

The mark  $\star$  shows major revised points.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

# NEC Electronics Inc. (U.S.)

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC Electronics (Germany) GmbH

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.** Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

NEC Electronics Italiana s.r.l. Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### **NEC Electronics (France) S.A.** Velizy-Villacoublay, France

Tel: 01-3067-5800 Fax: 01-3067-5899

#### **NEC Electronics (France) S.A.**

Madrid Office Madrid, Spain Tel: 091-504-2787 Fax: 091-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. Novena Square, Singapore Tel: 253-8311 Fax: 250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP, Brasil Tel: 11-6462-6810 Fax: 11-6462-6829

# INTRODUCTION

|   | Target Readers | : This manual is intended for users who wish to understand the functions of 78K/IV                                                                                           |

|---|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                | Series products, and design and develop application systems using these products.                                                                                            |

|   |                |                                                                                                                                                                              |

|   |                | 78K/IV Series products                                                                                                                                                       |

|   |                | • μPD784026 Subseries : μPD784020, 784021, 784025, 784026, 78P4026                                                                                                           |

|   |                | <ul> <li>μPD784038 Subseries</li> <li>μPD784031, 784035, 784036, 784037, 784038,<br/>78P4038, 784031(A), 784035(A), 784036(A)</li> </ul>                                     |

|   |                | • μPD784038Y Subseries : μPD784031Y, 784035Y, 784036Y, 784037Y, 784038Y, 78P4038Y                                                                                            |

|   |                | <ul> <li>μPD784046 Subseries</li> <li>μPD784044, 784046, 784054, 78F4046, 78444(A),</li> <li>(A1), (A2), μPD784046(A), (A1), (A2), 784054(A),</li> <li>(A1), (A2)</li> </ul> |

| * |                | • μPD784216A Subseries : μPD784214A, 784215A, 784216A, 78F4216A                                                                                                              |

| * |                | • μPD784216AY Subseries : μPD784214AY, 784215AY, 784216AY, 78F4216AY                                                                                                         |

| * |                | • μPD784218A Subseries <sup>Note</sup> : μPD784217A, 784218A, 78F4218A                                                                                                       |

| * |                | <ul> <li>μPD784218AY Subseries<sup>Note</sup> : μPD784217AY, 784218AY, 78F4218AY</li> </ul>                                                                                  |

|   |                | • μPD784225 Subseries : μPD784224, 784225, 78F4225                                                                                                                           |

|   |                | • μPD784225Y Subseries : μPD784224Y, 784225Y, 78F4225Y                                                                                                                       |

|   |                | • μPD784908 Subseries : μPD784907, 784908, 78P4908                                                                                                                           |

| * |                | • μPD784915 Subseries : μPD784915B, 784916B, 78P4916                                                                                                                         |

| * |                | • μPD784928 Subseries : μPD784927, 784928, 78F4928 <sup>Note</sup>                                                                                                           |

| * |                | • μPD784928Y Subseries : μPD784927Y, 784928Y, 78F4928Y <sup>Note</sup>                                                                                                       |

| * |                | • μPD784938A Subseries : μPD784935A, 784936A, 784937A, 784938A, 78F4938A <sup>Note</sup>                                                                                     |

| * |                | • μPD784956A Subseries <sup>Note</sup> :μPD784953A, 784956A, 78F4956A <sup>Note</sup>                                                                                        |

| * |                | • μPD784976A Subseries <sup>Note</sup> : μPD784975A <sup>Note</sup> , 78F4976A <sup>Note</sup>                                                                               |

|   |                | Note Under development                                                                                                                                                       |

|   | Purpose        | : This manual is intended for users to understand the instruction functions of the 78K/IV Series.                                                                            |

|   | Organization   | : This manual consists of the following chapters.                                                                                                                            |

|   |                | Features of 78K/IV Series products     ODU functions                                                                                                                         |

|   |                | <ul><li>CPU functions</li><li>Instruction set</li></ul>                                                                                                                      |

|   |                | Instruction set     Instruction descriptions                                                                                                                                 |

|   |                | Development tools                                                                                                                                                            |

|   |                |                                                                                                                                                                              |

| How to Read This Manual | : It is assumed that the reader o electrical engineering, logic cire                                                                                                                                                         |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                           |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | <ul> <li>To check the details of an instr<br/>→ Use APPENDIX A and API</li> </ul>                                                                                                                                            |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                           |

|                         | <ul> <li>To check an instruction when a mnemonic:</li> <li>→ Find the mnemonic in CHAP in CHAPTER 7 DESCRIPT</li> </ul>                                                                                                      | PTER 6 INSTRUCT                                                                                                                                                                                            | <b>ION SET</b> , then check the function                                                                                                                                                                                                                                  |

|                         | <ul> <li>For a general understanding of<br/>→ Read in accordance with th</li> </ul>                                                                                                                                          |                                                                                                                                                                                                            | on functions of the 78K/IV Series:                                                                                                                                                                                                                                        |

| *<br>*<br>*             | <ul> <li>μPD784046 Subseries U</li> <li>μPD784054 User's Man</li> <li>μPD784216A, 784216A</li> <li>Hardware (U12015E)</li> <li>μPD784225, 784225Y S</li> <li>μPD784908 Subseries U</li> <li>μPD784915 Subseries U</li> </ul> | Manual.<br>Jser's Manual – Ha<br>ubseries User's Ma<br>ual – Hardware (U1<br>Y, 784218A, 78421<br>ubseries User's Ma<br>Jser's Manual – Ha<br>ubseries User's Ma<br>User's Manual – H<br>User's Manual – H | ardware (U10898E)<br>anual – Hardware (U11316E)<br>ardware (U11515E)<br>11719E)<br>8AY Subseries User's Manual –<br>anual – Hardware (U12679E)<br>ardware (U11787E)<br>ardware (U10444E)<br>anual – Hardware (U12648E)<br>lardware (To be prepared)<br>lardware (U14395E) |

| Conventions             | Active low representation:Note:Caution:Remark:                                                                                                                                                                               | ××× (overscore over<br>Footnote for item r                                                                                                                                                                 | and lower digit on right<br>er pin or signal name)<br>marked with <b>Note</b> in the text<br>ng particular attention<br>ormation<br>xxxxB or xxxx<br>xxxx<br>xxxxH                                                                                                        |

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### • Documents common to the 78K/IV Series

| Document Name                      | Document Number |

|------------------------------------|-----------------|

| User's Manual – Instructions       | This manual     |

| Application Note – Software Basics | U10095E         |

#### • Individual documents

#### • µPD784026 Subseries

| Document Name                                          | Document Number |

|--------------------------------------------------------|-----------------|

| μPD784020, 84021 Data Sheet                            | U11514E         |

| μPD784025, 784026 Data Sheet                           | U11605E         |

| μPD78P4026 Data Sheet                                  | U11609E         |

| μPD784026 Subseries User's Manual – Hardware           | U10898E         |

| µPD784026 Subseries Application Note – Hardware Basics | U10573E         |

# • µPD784038, 784038Y Subseries

| Document Name                                         | Document Number |

|-------------------------------------------------------|-----------------|

| µPD784031 Data Sheet                                  | U11507E         |

| μPD784035, 784036, 784037, 784038 Data Sheet          | U10847E         |

| µPD784031(A) Data Sheet                               | U13009E         |

| μPD784035(A), 784036(A) Data Sheet                    | U13010E         |

| μPD78P4038 Data Sheet                                 | U10848E         |

| µPD784031Y Data Sheet                                 | U11504E         |

| µPD784035Y, 784036Y, 784037Y, 784038Y Data Sheet      | U10741E         |

| µPD78P4038Y Data Sheet                                | U10742E         |

| µPD784038, 784038Y Subseries User's Manual – Hardware | U11316E         |

#### • *µ***PD784046 Subseries**

| Document Name                                | Document Number |

|----------------------------------------------|-----------------|

| μPD784044, 784046 Data Sheet                 | U10951E         |

| μPD784044(A), 784046(A) Data Sheet           | U13121E         |

| µPD784054 Data Sheet                         | U11154E         |

| µPD784054(A) Data Sheet                      | U13122E         |

| µPD78F4046 Preliminary Product Information   | U11447E         |

| μPD784046 Subseries User's Manual – Hardware | U11515E         |

| $\mu$ PD784054 User's Manual – Hardware      | U11719E         |

# • $\mu$ PD784216A, 784216AY, 784218A, 784218AY Subseries

| Document Name                                                                                               | Document Number |

|-------------------------------------------------------------------------------------------------------------|-----------------|

| μPD784214A, 784215A, 784216A, 784217A, 784218A, 784214AY, 784215AY, 784216AY, 784217AY, 784218AY Data Sheet | U14121E         |

| µPD78F4216A, 78F4216AY, 78F4218A, 78F4218AY Data Sheet                                                      | U14125E         |

| µPD784216A, 784216AY Subseries User's Manual – Hardware                                                     | U12015E         |

# • μPD784225, 784225Y Subseries

| Document Name                                         | Document Number |

|-------------------------------------------------------|-----------------|

| μPD784224, 784225, 784224Y, 784225Y Data Sheet        | U12376E         |

| µPD78F4225 Preliminary Product Information            | U12499E         |

| µPD78F4225Y Preliminary Product Information           | U12377E         |

| μPD784225, 784225Y Subseries User's Manual – Hardware | U12679E         |

# • µPD784908 Subseries

| Document Name                                | Document Number |

|----------------------------------------------|-----------------|

| μPD784907, 784908 Data Sheet                 | U11680E         |

| µPD78P4908 Data Sheet                        | U11681E         |

| μPD784908 Subseries User's Manual – Hardware | U11787E         |

## • *µ*PD784915 Subseries

| Document Name                                                            | Document Number |

|--------------------------------------------------------------------------|-----------------|

| μPD784915B, 784916B Data Sheet                                           | U13118E         |

| µPD78P4916 Data Sheet                                                    | U11045E         |

| µPD784915 Subseries User's Manual – Hardware                             | U10444E         |

| µPD784915, 784928, 784928Y Subseries Application Note – VCR Servo Basics | U11361E         |

# \* • μPD784928, 784928Y Subseries

| Document Name                                         | Document Number |

|-------------------------------------------------------|-----------------|

| μPD784927, 784928, 784927Y, 784928Y Data Sheet        | U12255E         |

| µPD78F4928 Preliminary Product Information            | U12188E         |

| µPD78F4928Y Preliminary Product Information           | U12271E         |

| µPD784928, 784928Y Subseries User's Manual – Hardware | U12648E         |

## \* • μPD784938A Subseries

| Document Name                                    | Document Number |

|--------------------------------------------------|-----------------|

| μPD784935A, 784936A, 784937A, 784938A Data Sheet | U13572E         |

| μPD78F4938A Data Sheet                           | To be prepared  |

| µPD784938A Subseries User's Manual – Hardware    | To be prepared  |

# \* • μPD784956A Subseries

| Document Name                                       | Document Number |

|-----------------------------------------------------|-----------------|

| μPD784953A, 784956A Preliminary Product Information | To be prepared  |

| µPD78F4956A Preliminary Product Information         | To be prepared  |

| µPD784956A Subseries User's Manual – Hardware       | To be prepared  |

## \* • μPD784976A Subseries

| Document Name                                 | Document Number |

|-----------------------------------------------|-----------------|

| μPD784975A Data Sheet                         | On preparation  |

| μPD78F4976A Data Sheet                        | To be prepared  |

| µPD784976A Subseries User's Manual – Hardware | U15017E         |

# CONTENTS

| 1.1 |       | V Series Product Lineup                   |

|-----|-------|-------------------------------------------|

| 1.2 | Produ | uct Outline of $\mu$ PD784026 Subseries   |

|     | 1.2.1 | Features                                  |

|     | 1.2.2 | Applications                              |

|     | 1.2.3 | Ordering information and quality grade    |

|     | 1.2.4 | Outline of functions                      |

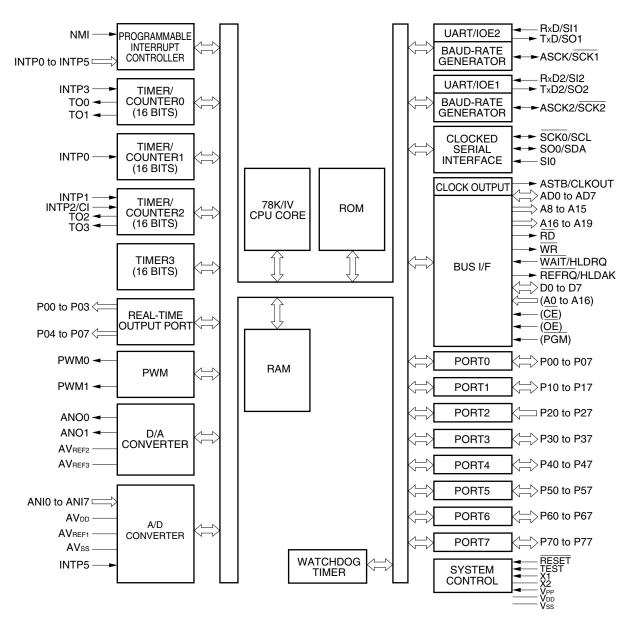

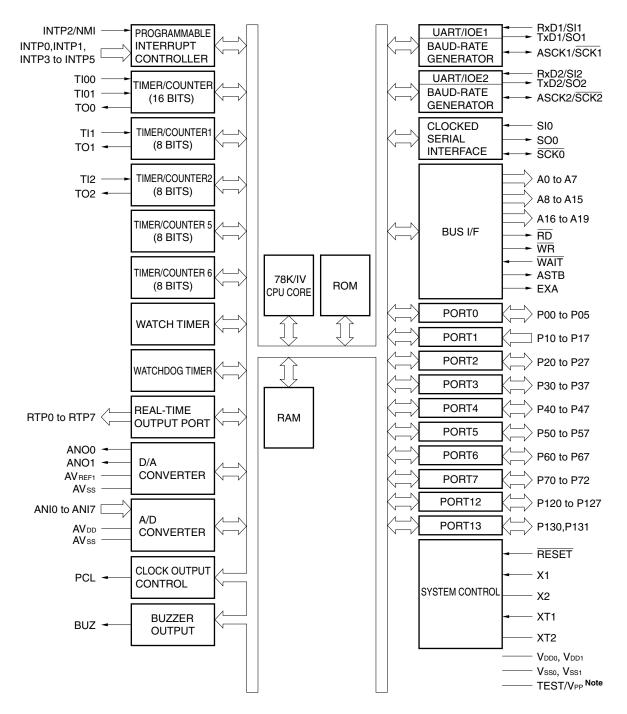

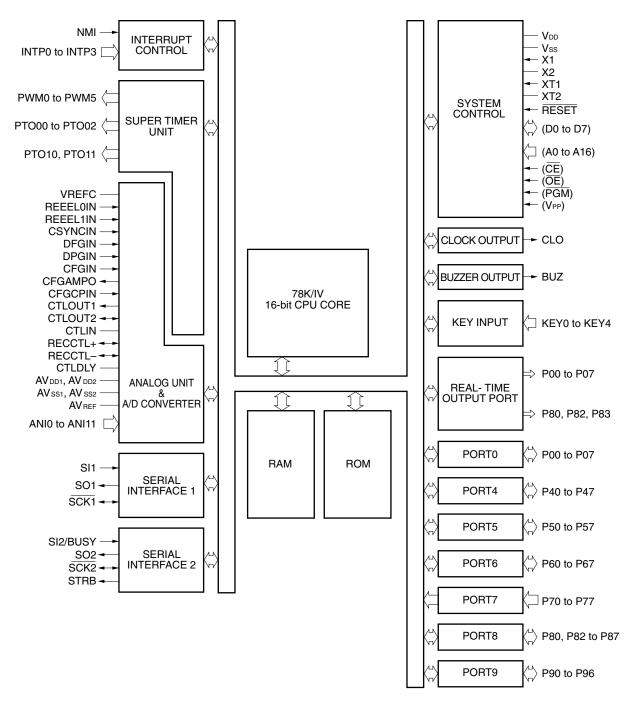

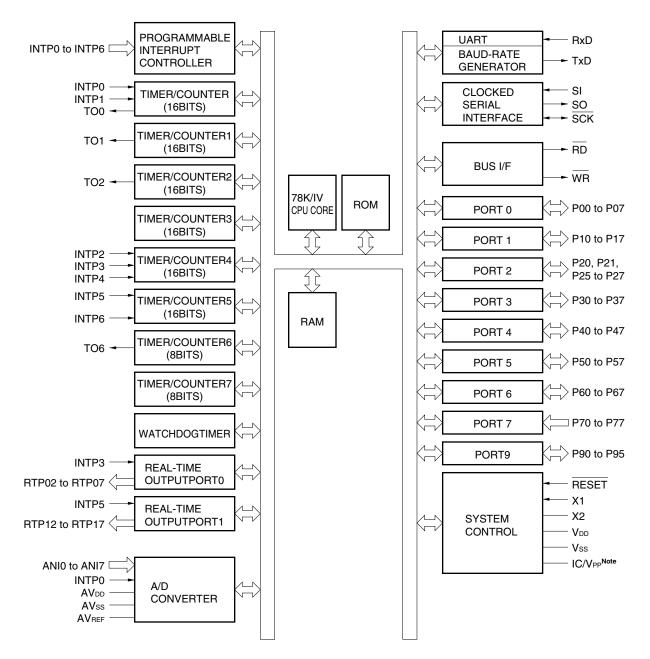

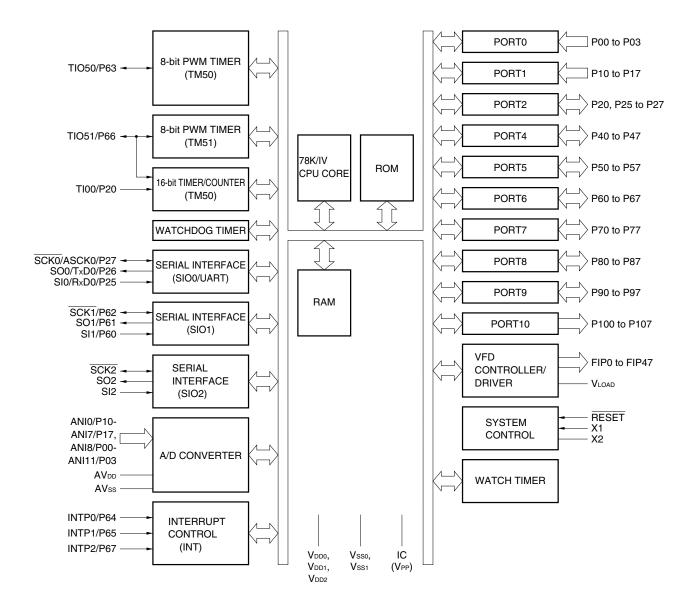

|     | 1.2.5 | Block diagram                             |

| 1.3 | Produ | uct Outline of $\mu$ PD784038 Subseries   |

|     | 1.3.1 | Features                                  |

|     | 1.3.2 | Applications                              |

|     | 1.3.3 | Ordering information and quality grade    |

|     | 1.3.4 | Outline of functions                      |

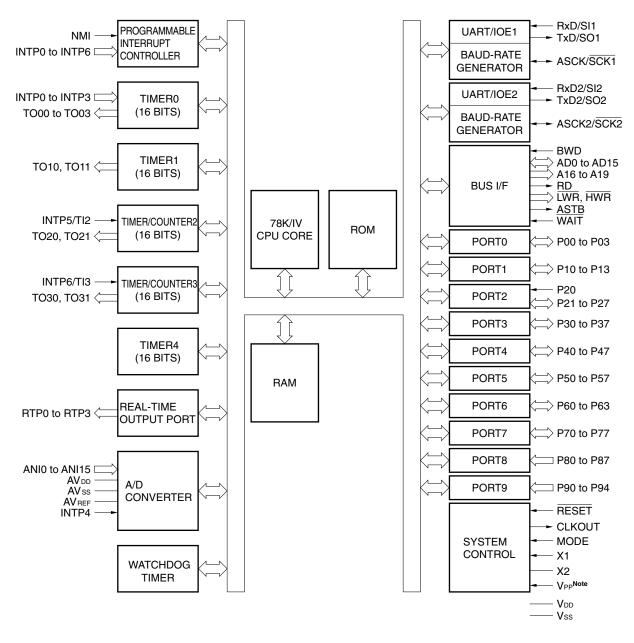

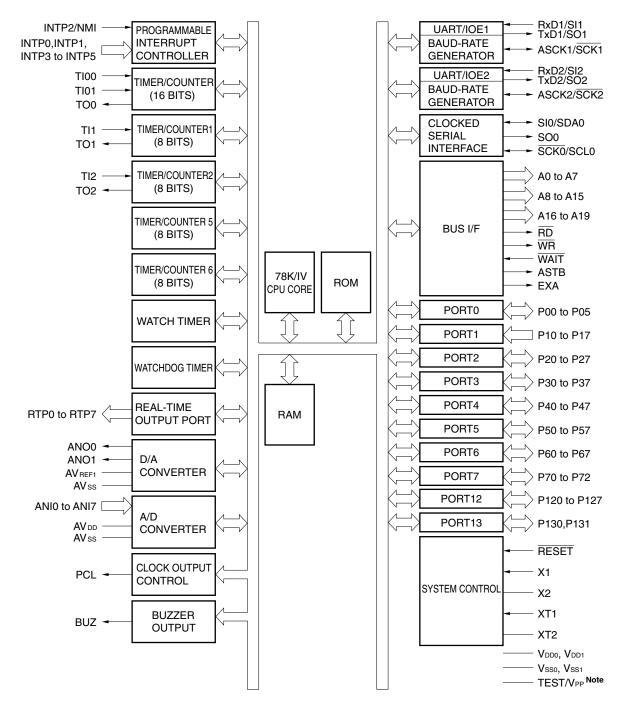

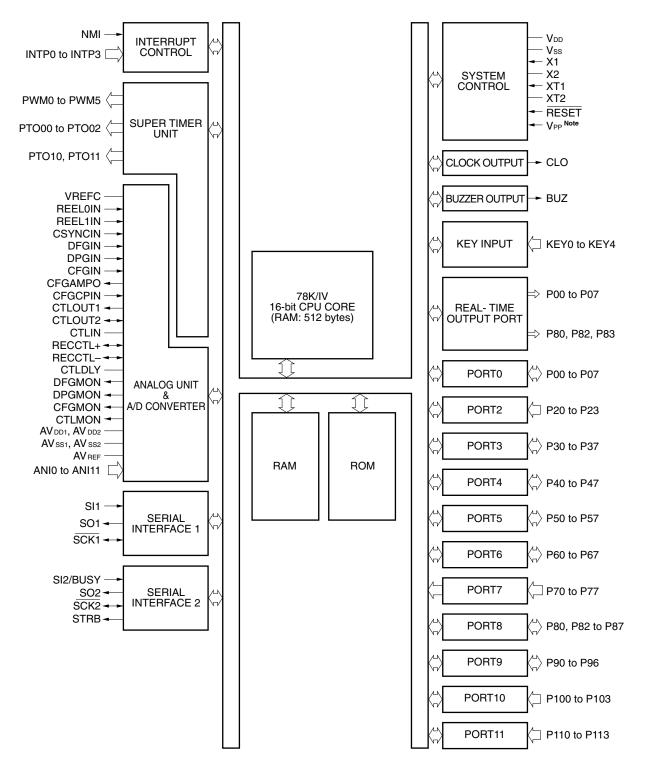

|     | 1.3.5 | Block diagram                             |

| 1.4 |       | uct Outline of $\mu$ PD784038Y Subseries  |

|     | 1.4.1 | Features                                  |

|     | 1.4.2 | Applications                              |

|     | 1.4.3 | Ordering information and quality grade    |

|     | 1.4.4 | Outline of functions                      |

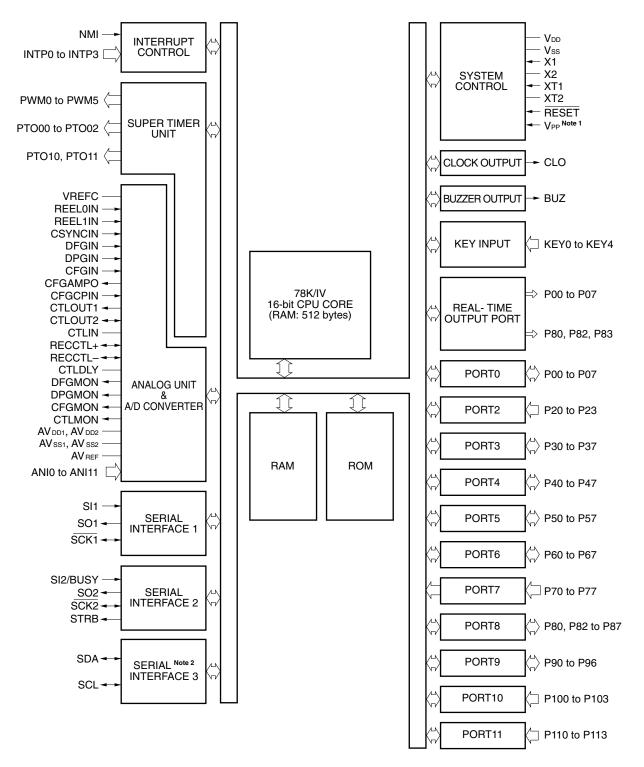

|     | 1.4.5 | Block diagram                             |

| 1.5 | Produ | uct Outline of $\mu$ PD784046 Subseries   |

|     | 1.5.1 | Features                                  |

|     | 1.5.2 | Applications                              |

|     | 1.5.3 | Ordering information and quality grade    |

|     | 1.5.4 | Outline of functions                      |

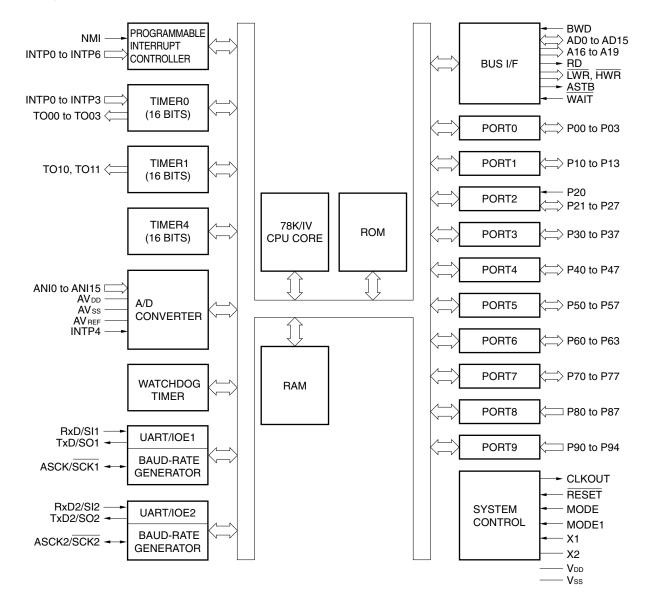

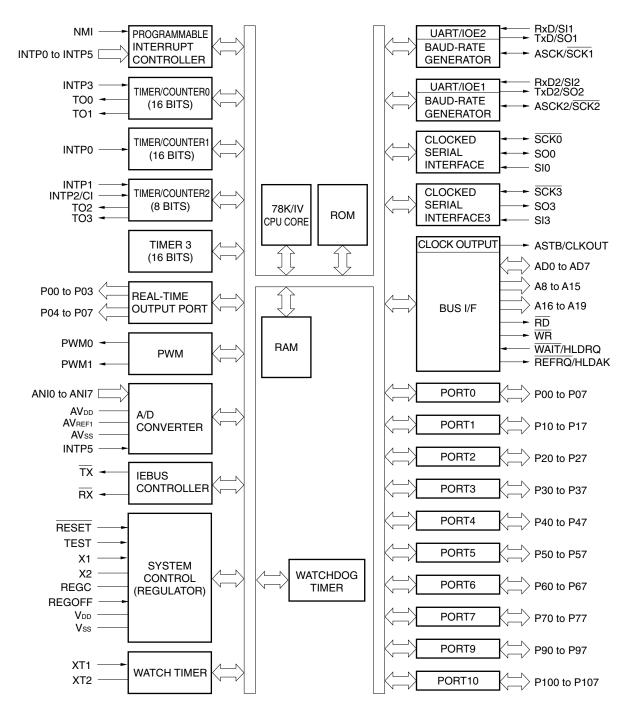

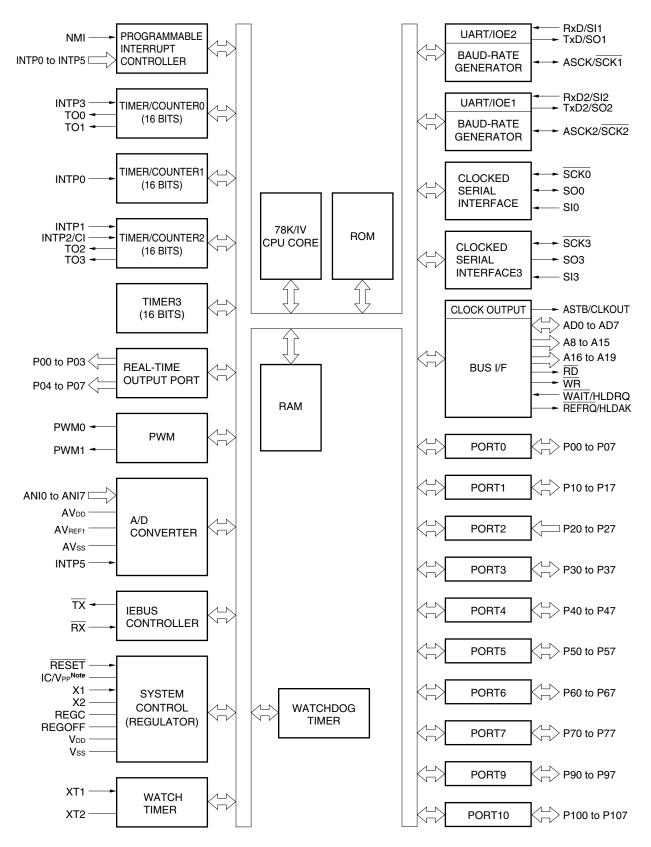

|     | 1.5.5 | Block diagram                             |

| 1.6 | Produ | uct Outline of $\mu$ PD784216A Subseries  |

|     | 1.6.1 | Features                                  |

|     | 1.6.2 | Applications                              |

|     | 1.6.3 | Ordering information and quality grade    |

|     | 1.6.4 | Outline of functions                      |

|     | 1.6.5 | Block diagram                             |

| 1.7 | Produ | uct Outline of $\mu$ PD784216AY Subseries |

|     | 1.7.1 | Features                                  |

|     | 1.7.2 | Applications                              |

|     | 1.7.3 | Ordering information and quality grade    |

|     | 1.7.4 | Outline of functions                      |

|     | 1.7.5 | Block diagram                             |

| 1.8 | Produ | uct Outline of $\mu$ PD784218A Subseries  |

|     | 1.8.1 | Features                                  |

|     | 1.8.2 | Applications                              |

|     | 1.8.3 | Ordering information and quality grade    |

|     | 1.8.4 | Outline of functions                      |

|     | 1.8.5 | Block diagram                             |

| 1.9  | Produ  | ct Outline of $\mu$ PD784218AY Subseries | 57 |

|------|--------|------------------------------------------|----|

|      | 1.9.1  | Features                                 | 57 |

|      | 1.9.2  | Applications                             | 58 |

|      | 1.9.3  | Ordering information and quality grade   | 58 |

|      | 1.9.4  | Outline of functions                     | 59 |

|      | 1.9.5  | Block diagram                            | 61 |

| 1.10 | Produ  | ct Outline of $\mu$ PD784225 Subseries   | 62 |

|      | 1.10.1 | Features                                 | 62 |

|      | 1.10.2 | Applications                             | 63 |

|      | 1.10.3 | Ordering information and quality grade   | 63 |

|      | 1.10.4 | Outline of functions                     | 64 |

|      | 1.10.5 | Block diagram                            | 66 |

| 1.11 | Produ  | ct Outline of $\mu$ PD784225Y Subseries  | 67 |

|      | 1.11.1 | Features                                 | 6  |

|      | 1.11.2 | Applications                             | 68 |

|      | 1.11.3 | Ordering information and quality grade   | 68 |

|      | 1.11.4 | Outline of functions                     | 6  |

|      | 1.11.5 | Block diagram                            | 7  |

| 1.12 | Produ  | ct Outline of $\mu$ PD784908 Subseries   | 72 |

|      | 1.12.1 | Features                                 | 72 |

|      | 1.12.2 | Applications                             | 7  |

|      | 1.12.3 | Ordering information and quality grade   | 7  |

|      | 1.12.4 | Outline of functions                     | 74 |

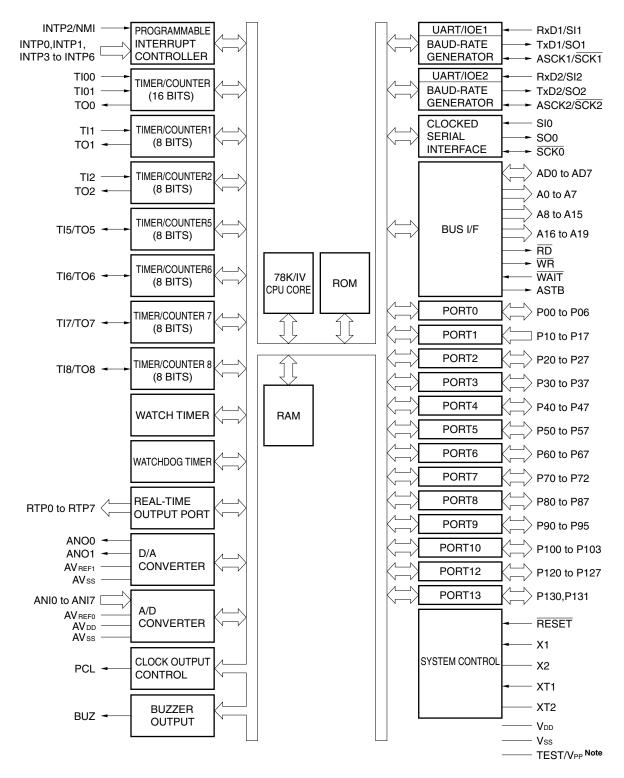

|      | 1.12.5 | Block diagram                            | 70 |

| 1.13 | Produ  | ct Outline of $\mu$ PD784915 Subseries   | 77 |

|      | 1.13.1 | Features                                 | 7  |

|      | 1.13.2 | Applications                             | 7  |

|      | 1.13.3 | Ordering information and quality grade   | 78 |

|      | 1.13.4 | Outline of functions                     | 79 |

|      | 1.13.5 | Block diagram                            | 8  |

| 1.14 | Produ  | ct Outline of $\mu$ PD784928 Subseries   | 8  |

|      | 1.14.1 | Features                                 | 8  |

|      | 1.14.2 | Applications                             | 8  |

|      | 1.14.3 | Ordering information                     | 8  |

|      | 1.14.4 | Outline of functions                     | 8  |

|      | 1.14.5 | Block diagram                            | 8  |

| 1.15 | Produ  | ct Outline of $\mu$ PD784928Y Subseries  | 8  |

|      | 1.15.1 | Features                                 | 8  |

|      | 1.15.2 | Applications                             | 8  |

|      | 1.15.3 | Ordering information                     | 8  |

|      | 1.15.4 | Outline of functions                     | 8  |

|      | 1.15.5 | Block diagram                            | 8  |

| 1.16 | Produ  | ct Outline of $\mu$ PD784938A Subseries  | 89 |

|      | 1.16.1 | Features                                 | 8  |

|      | 1.16.2 | Applications                             | 8  |

|      | 1.16.3 | Ordering information and quality grade   | 9  |

|      | 1.16.4 | Outline of functions                     | 9  |

|      | 1.16.5 | Block diagram                            | 9  |

$\star$

| *  | 1.17  | Produ   | ct Outline of $\mu$ PD784956A Subseries | 94  |

|----|-------|---------|-----------------------------------------|-----|

|    |       | 1.17.1  | Features                                | 94  |

|    |       | 1.17.2  | Applications                            | 94  |

|    |       | 1.17.3  | Ordering information and quality grade  | 95  |

|    |       | 1.17.4  | Outline of functions                    | 96  |

|    |       | 1.17.5  | Block diagram                           | 98  |

| *  | 1.18  | Produ   | ct Outline of $\mu$ PD784976A Subseries | 99  |

|    |       | 1.18.1  | Features                                | 99  |

|    |       | 1.18.2  | Applications                            | 99  |

|    |       | 1.18.3  | Ordering information and quality grade  | 100 |

|    |       | 1.18.4  | Outline of functions                    | 101 |

|    |       | 1.18.5  | Block diagram                           | 103 |

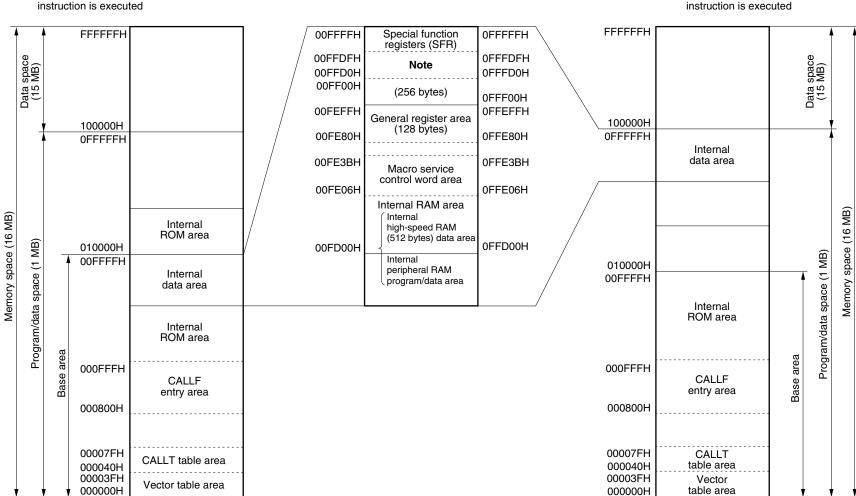

| CI | HAPTE | R2 M    | EMORY SPACE                             | 104 |

|    | 2.1   | Memo    | ry Space                                | 104 |

|    | 2.2   | Interna | al ROM Area                             | 106 |

|    | 2.3   |         |                                         | 108 |

|    |       | 2.3.1   | Vector table area                       | 109 |

|    |       | 2.3.2   | CALLT instruction table area            | 109 |

|    |       | 2.3.3   | CALLF instruction entry area            | 109 |

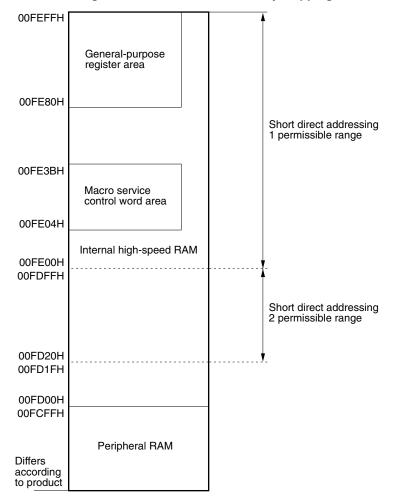

|    | 2.4   | Interna | al Data Area                            | 110 |

|    |       | 2.4.1   | Internal RAM area                       | 110 |

|    |       | 2.4.2   | Special function register (SFR) area    | 115 |

|    |       | 2.4.3   |                                         | 115 |

|    | 2.5   | Extern  |                                         | 115 |

|    |       |         |                                         |     |

| Cl | HAPTE | -       |                                         | 116 |

|    | 3.1   |         | 5                                       | 116 |

|    |       | 3.1.1   |                                         | 116 |

|    |       | 3.1.2   |                                         | 116 |

|    |       | 3.1.3   |                                         | 120 |

|    |       | 3.1.4   |                                         | 124 |

|    | 3.2   | Gener   | al-Purpose Registers                    | 128 |

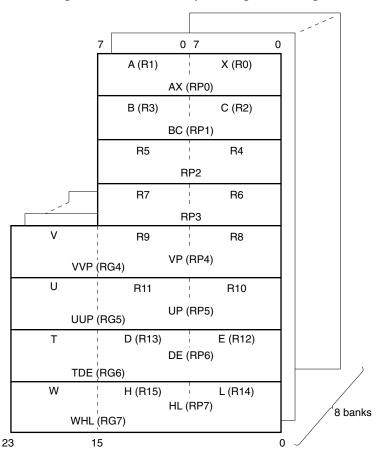

|    |       | 3.2.1   |                                         | 128 |

|    |       | 3.2.2   |                                         | 130 |

|    | 3.3   | Specia  | al Function Registers (SFR)             | 133 |

| CI | HAPTE | R4 IN   | ITERRUPT FUNCTIONS                      | 134 |

|    | 4.1   | Kinds   | of Interrupt Request                    | 135 |

|    |       | 4.1.1   | Software interrupt requests             | 135 |

|    |       | 4.1.2   | Non-maskable interrupt requests         | 135 |

|    |       | 4.1.3   | Maskable interrupt requests             | 135 |

|    | 4.2   | Interru | upt Service Modes                       | 136 |

|    |       | 4.2.1   | Vectored interrupts                     | 136 |

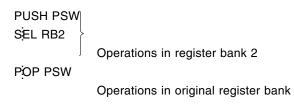

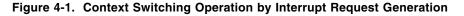

|    |       | 4.2.2   | Context switching                       | 136 |

|    |       | 4.2.3   | Macro service function                  | 137 |

| CHAPTE | R 5 AI  | DDRESSING                                           | 138 |

|--------|---------|-----------------------------------------------------|-----|

| 5.1    | Instruc | ction Address Addressing                            | 138 |

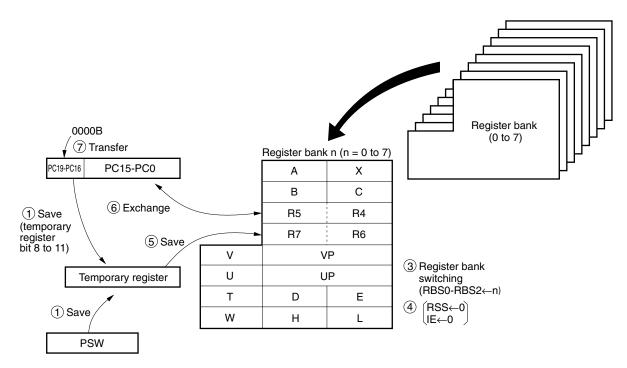

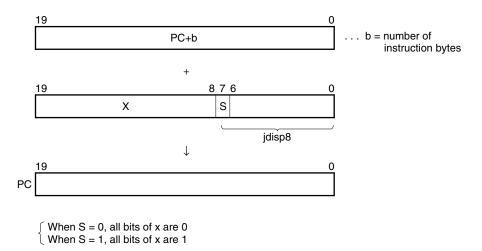

|        | 5.1.1   | Relative addressing                                 | 139 |

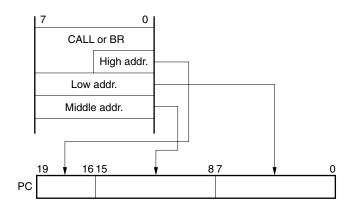

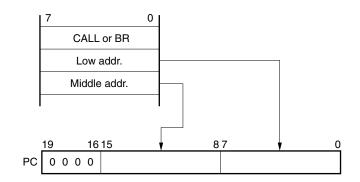

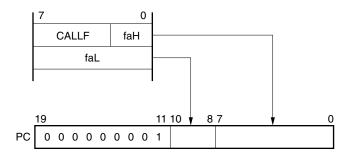

|        | 5.1.2   | Immediate addressing                                | 140 |

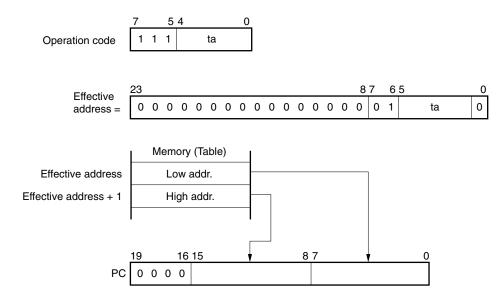

|        | 5.1.3   | Table indirect addressing                           | 142 |

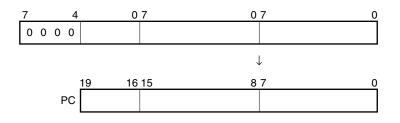

|        | 5.1.4   | 16-bit register addressing                          | 143 |

|        | 5.1.5   | 20-bit register addressing                          | 143 |

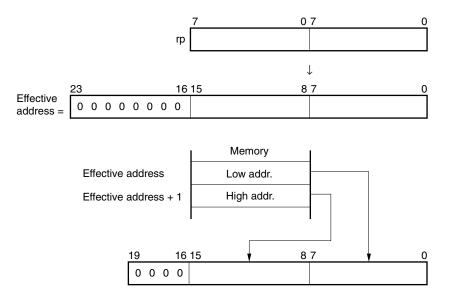

|        | 5.1.6   | 16-bit register indirect addressing                 | 144 |

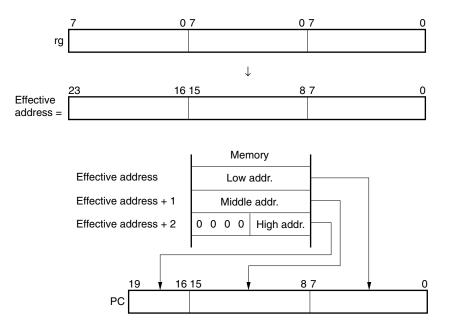

|        | 5.1.7   | 20-bit register indirect addressing                 | 145 |

| 5.2    | Opera   | nd Address Addressing                               | 146 |

|        | 5.2.1   | Implied addressing                                  | 147 |

|        | 5.2.2   | Register addressing                                 | 148 |

|        | 5.2.3   | Immediate addressing                                | 149 |

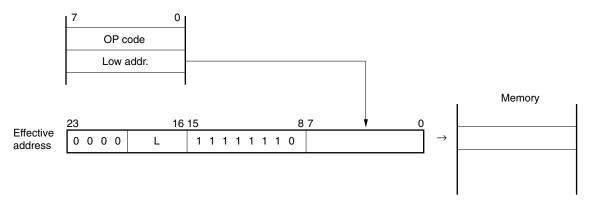

|        | 5.2.4   | 8-bit direct addressing                             | 150 |

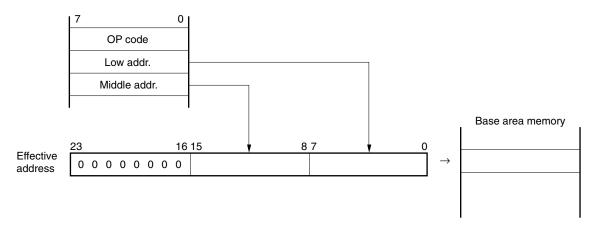

|        | 5.2.5   | 16-bit direct addressing                            | 151 |

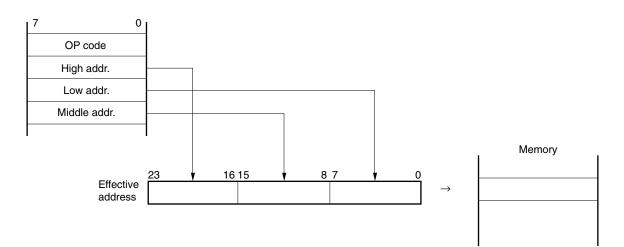

|        | 5.2.6   | 24-bit direct addressing                            | 152 |

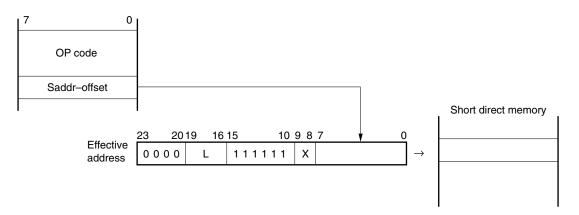

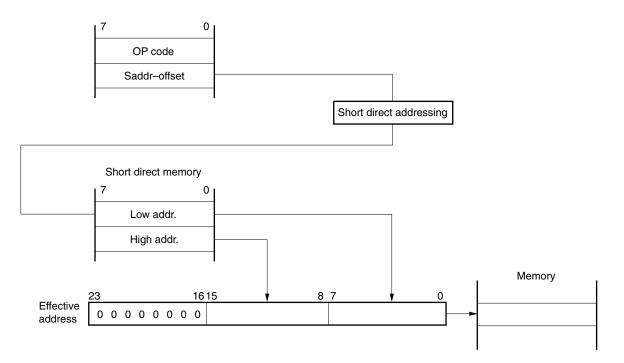

|        | 5.2.7   | Short direct addressing                             | 153 |

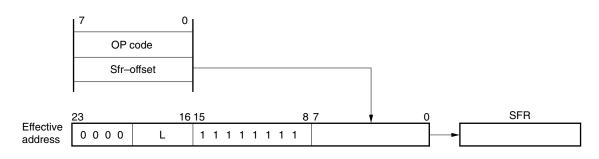

|        | 5.2.8   | Special function register (SFR) addressing function | 155 |

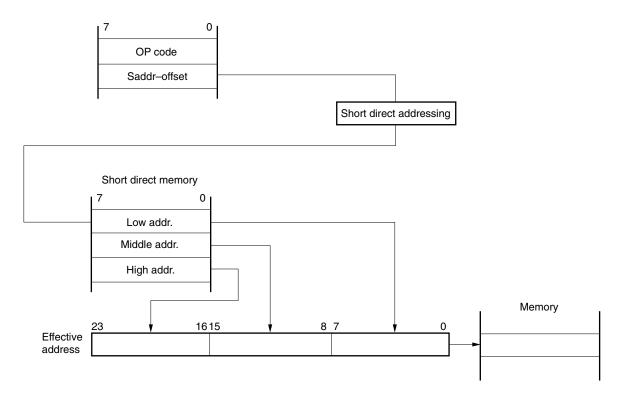

|        | 5.2.9   | Short direct 16-bit memory indirect addressing      | 156 |

|        | 5.2.10  | Short direct 24-bit memory indirect addressing      | 157 |

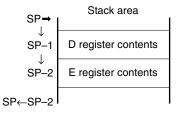

|        | 5.2.11  | Stack addressing                                    | 158 |

|        | 5.2.12  | 24-bit register indirect addressing                 | 159 |

|        | 5.2.13  | 16-bit register indirect addressing                 | 161 |

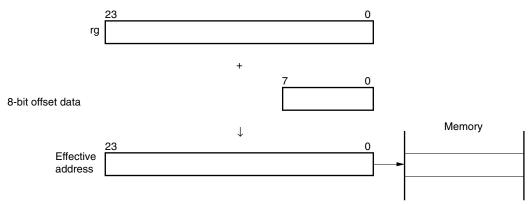

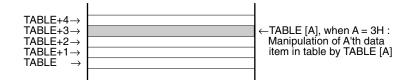

|        | 5.2.14  | Based addressing                                    | 162 |

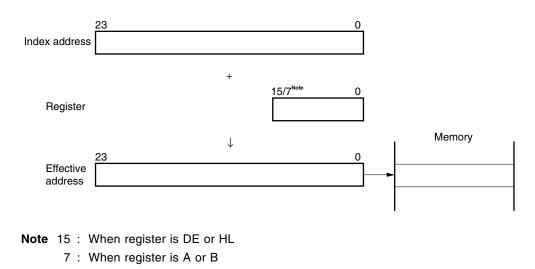

|        | 5.2.15  | Indexed addressing                                  | 163 |

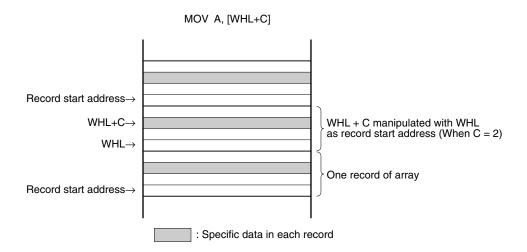

|        | 5.2.16  | Based indexed addressing                            | 164 |

|        |         |                                                     |     |

| СНАРТЕ | R6 IN   | STRUCTION SET                                       | 166 |

| 6.1    |         | d                                                   | 166 |

| 6.2    | -       | Instruction Operations                              | 170 |

| 6.3    |         | ctions Listed by Type of Addressing                 | 196 |

| 6.4    |         | tion Codes                                          | 201 |

|        | 6.4.1   | Operation code symbols                              | 201 |

|        | 6.4.2   | List of operation codes                             | 204 |

| 6.5    | ••••    | er of Instruction Clocks                            | 262 |

|        | 6.5.1   | Execution time of instruction                       | 262 |

|        | 6.5.2   | Legend for "Clocks" column                          | 262 |

|        | 6.5.3   | Explanation of "Clocks" column                      | 263 |

|        | 6.5.4   | List of number of clocks                            | 264 |

|        | 0.0.1   |                                                     | 201 |

| СНАРТЕ | B7 D    | ESCRIPTION OF INSTRUCTIONS                          | 294 |

| 7.1    |         | vata Transfer Instruction                           | 296 |

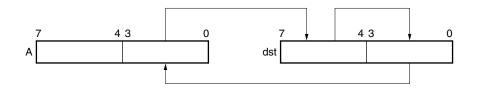

| 7.2    |         | Data Transfer Instruction                           | 299 |

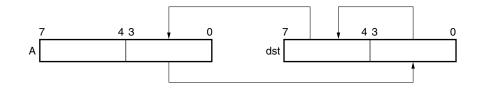

| 7.2    |         | Data Transfer Instruction                           | 302 |

| 7.4    |         | bata Exchange Instruction                           | 304 |

| 7.4    |         | Data Exchange Instruction                           | 304 |

| 7.6    |         | Deration Instructions                               | 308 |

| 7.0    |         | Operation Instructions                              | 318 |

| 1.1    | 10-010  |                                                     | 510 |

| 7.8    | 24-bit Operation Instructions                              | 325 |

|--------|------------------------------------------------------------|-----|

| 7.9    | Multiplication/Division Instructions                       | 328 |

| 7.10   | Special Operation Instructions                             | 334 |

| 7.11   | Increment/Decrement Instructions                           | 344 |

| 7.12   | Adjustment Instructions                                    | 351 |

| 7.13   | Shift/Rotate Instructions                                  | 355 |

| 7.14   | Bit Manipulation Instructions                              | 366 |

| 7.15   | Stack Manipulation Instructions                            | 377 |

| 7.16   | Call/Return Instructions                                   | 389 |

| 7.17   | Unconditional Branch Instruction                           | 403 |

| 7.18   | Conditional Branch Instructions                            | 405 |

| 7.19   | CPU Control Instructions                                   | 425 |

| 7.20   | Special Instructions                                       | 435 |

| 7.21   | String Instructions                                        | 438 |

|        |                                                            |     |

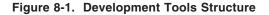

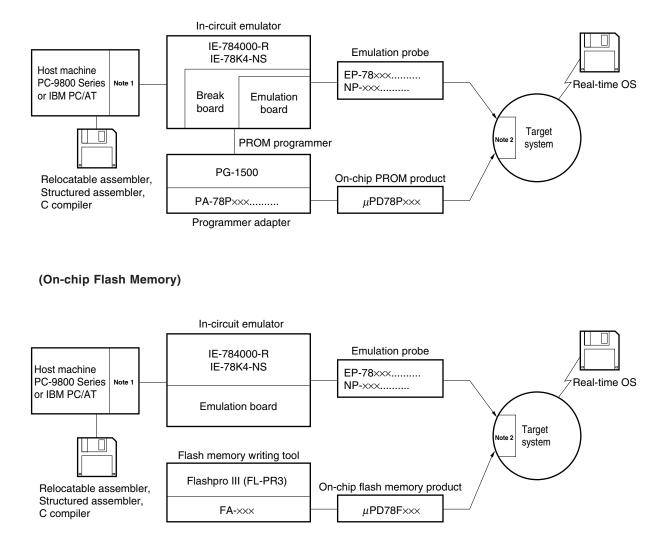

| CHAPTE | R 8 DEVELOPMENT TOOLS                                      | 475 |

| 8.1    | Development Tools                                          | 476 |

| 8.2    | PROM Programming Tools                                     | 479 |

| 8.3    | Flash Memory Programming Tools                             | 479 |

|        |                                                            |     |

| CHAPTE | R 9 EMBEDDED SOFTWARE                                      | 480 |

| 9.1    | Real-time OS                                               | 480 |

|        |                                                            |     |

| APPEND | IX A INDEX OF INSTRUCTIONS (MNEMONICS: BY FUNCTION)        | 481 |

|        |                                                            |     |

| APPEND | IX B INDEX OF INSTRUCTIONS (MNEMONICS: ALPHABETICAL ORDER) | 484 |

|        |                                                            |     |

| APPEND | IX C REVISION HISTORY                                      | 486 |

# LIST OF FIGURES

| Figure No | o. Title                                                    | Page |

|-----------|-------------------------------------------------------------|------|

| 1-1       | 78K Series and 78K/IV Series Composition                    | 20   |

| 2-1       | Memory Map                                                  | 105  |

| 2-2       | Internal RAM Memory Mapping                                 |      |

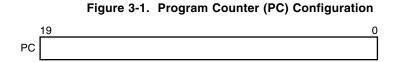

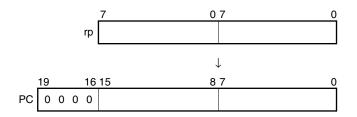

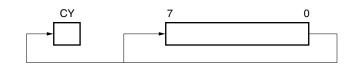

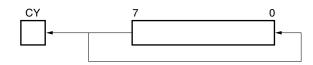

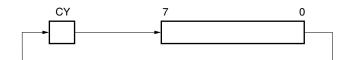

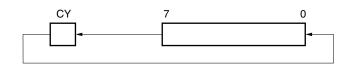

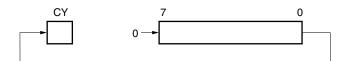

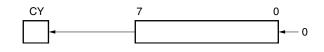

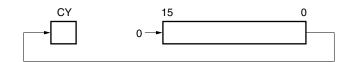

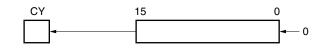

| 3-1       | Program Counter (PC) Configuration                          | 116  |

| 3-2       | Program Status Word (PSW) Configuration                     | 117  |

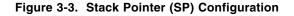

| 3-3       | Stack Pointer (SP) Configuration                            |      |

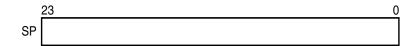

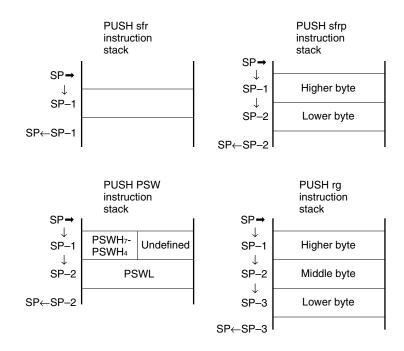

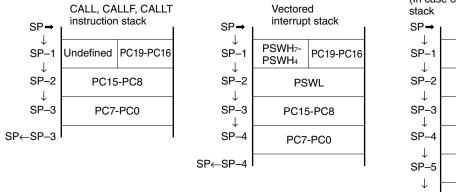

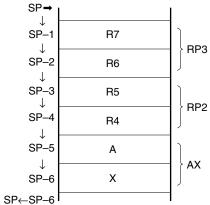

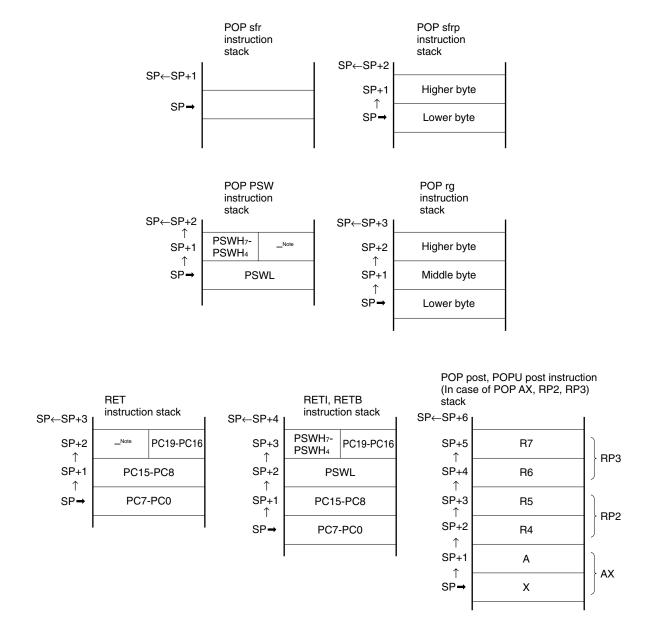

| 3-4       | Data Saved to Stack Area                                    | 125  |

| 3-5       | Data Restored from Stack Area                               | 126  |

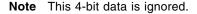

| 3-6       | General-Purpose Register Configuration                      | 128  |

| 3-7       | General-Purpose Register Addresses                          | 129  |

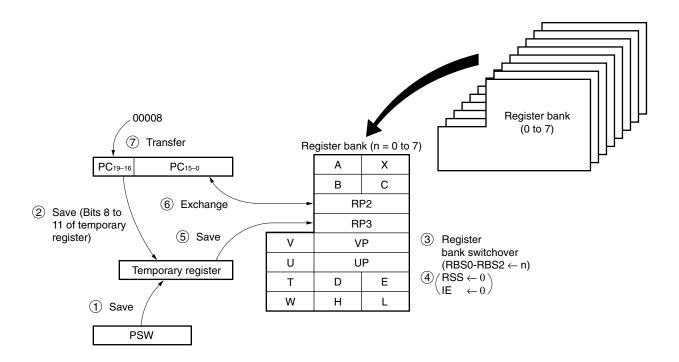

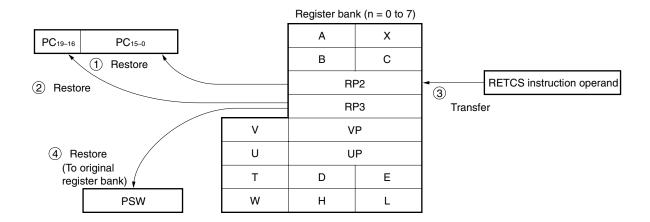

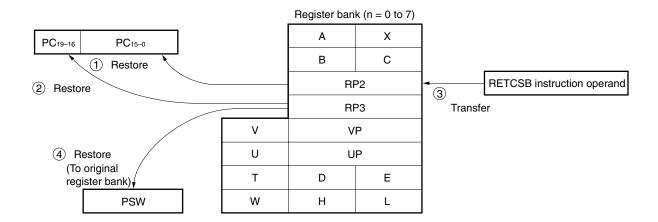

| 4-1       | Context Switching Operation by Interrupt Request Generation | 136  |

| 8-1       | Development Tools Structure                                 | 478  |

# LIST OF TABLES

| Table No. | Title                                                                         | Page |

|-----------|-------------------------------------------------------------------------------|------|

|           |                                                                               |      |

| 2-1       | List of Internal ROM Space for 78K/IV Series Products                         | 106  |

| 2-2       | Vector Table                                                                  | 109  |

| 2-3       | Internal RAM Area in 78K/IV Series Products                                   | 111  |

| 3-1       | Register Bank Selection                                                       | 119  |

| 3-2       | Function Names and Absolute Names                                             | 132  |

| 4-1       | Interrupt Request Servicing                                                   | 134  |

| 6-1       | List of Instructions by 8-Bit Addressing                                      | 196  |

| 6-2       | List of Instructions by 16-Bit Addressing                                     | 197  |

| 6-3       | List of Instructions by 24-Bit Addressing                                     | 198  |

| 6-4       | List of Instructions by Bit Manipulation Instruction Addressing               | 199  |

| 6-5       | List of Instructions by Call/Return Instruction/Branch Instruction Addressing | 200  |

| 8-1       | Types and Functions of Development Tools                                      | 476  |

# CHAPTER 1 FEATURES OF 78K/IV SERIES PRODUCTS

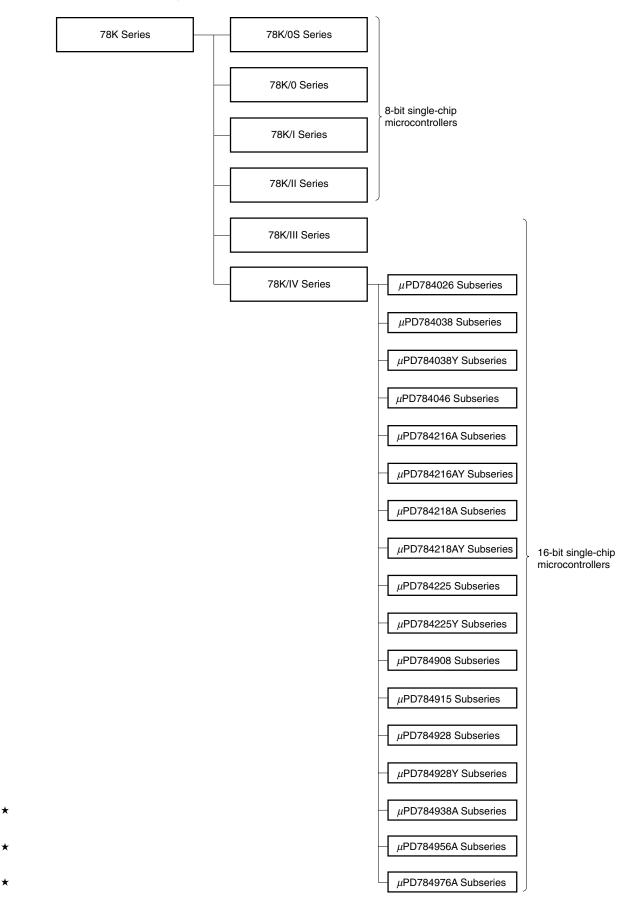

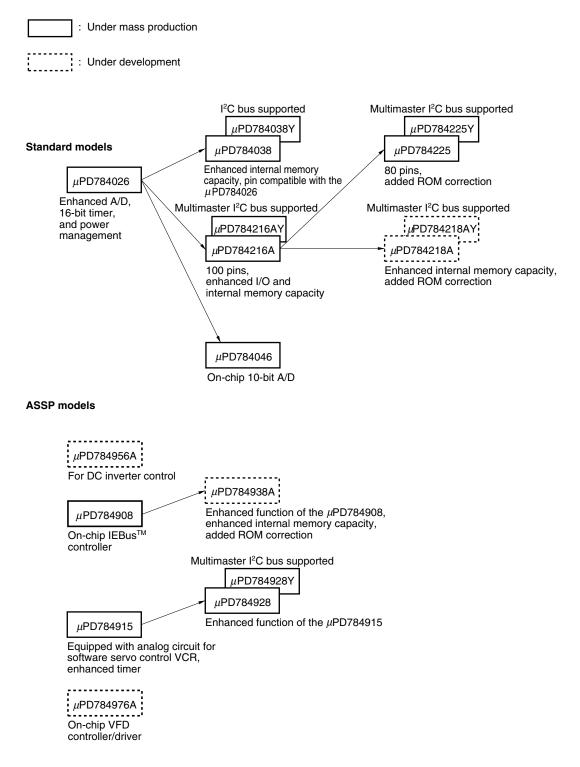

The 78K Series consists of 6 series as shown in Figure 1-1.

The 78K/IV Series is one of these 6 series, comprising products with an on-chip 16-bit CPU.

These products have an instruction set suitable for control applications, a high-performance interrupt controller, and incorporate a high-performance CPU equipped with a maximum 1 MB program memory space and maximum 16 MB data memory space.

The 78K/IV Series offers a variety of subseries, enabling the most suitable subseries to be selected for a particular application.

All the subseries have the same CPU, and differ only in their peripheral hardware. Consequently, the entire instruction set is common to all subseries. Moreover, individual products within a subseries differ only in the size of on-chip memory.

Figure 1-1. 78K Series and 78K/IV Series Composition

#### 1.1 78K/IV Series Product Lineup

\*

# 1.2 Product Outline of μPD784026 Subseries (μPD784020, 784021, 784025, 784026, 78P4026)

#### 1.2.1 Features

- Pins are compatible with µPD78234 Subseries

- Minimum instruction execution time: 160 ns/320 ns/640 ns/1,280 ns (at 25 MHz operation)

- On-chip memory

- ROM

Mask ROM : 48 KB (µPD784025)

| D784026) |

|----------|

|          |

None (µPD784020, 784021)

- PROM : 64 KB (μPD78P4026)

- RAM : 2,048 bytes (μPD784021, 784025, 784026)

512 bytes (µPD784020)

• I/O pins: 64

46 (μPD784020, 784021 only)

- Timer/counter: 16-bit timer/counter  $\times$  3 units

- 16-bit timer  $\times$  1 unit

- Watchdog timer: 1 channel

- A/D converter: 8-bit resolution  $\times$  8 channels

- D/A converter: 8-bit resolution × 2 channels

- Serial interface: 3 channels

UART/IOE (3-wire serial I/O): 2 channels (on-chip baud rate generator)

CSI (3-wire serial I/O, SBI): 1 channel

- Interrupt controller (4-level priority) Vectored interrupt/macro service/context switching

- Standby function: HALT/STOP/IDLE mode

- Clock output function Selectable from fclk, fclk/2, fclk/4, fclk/8, fclk/16 (except μPD784020, 784021)

- Power supply voltage: VDD = 2.7 to 5.5 V

#### 1.2.2 Applications

Laser beam printers, autofocus cameras, plain paper copiers, printers, electronic typewriters, air conditioners, electronic musical instruments, cellular phones, etc.

#### 1.2.3 Ordering information and quality grade

#### (1) Ordering information

| Part Number                    | Package                                              | Internal ROM                 |

|--------------------------------|------------------------------------------------------|------------------------------|

| μPD784020GC-3B9                | 80-pin plastic QFP (14 $	imes$ 14 mm)                | None                         |

| μPD784021GC-3B9                | 80-pin plastic QFP (14 $	imes$ 14 mm)                | None                         |

| μPD784021GK-BE9                | 80-pin plastic TQFP (fine pitch) (12 $\times$ 12 mm) | None                         |

| μPD784025GC-×××-3B9            | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Mask ROM                     |

| μPD784026GC-×××-3B9            | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Mask ROM                     |

| μPD78P4026GC-3B9               | 80-pin plastic QFP (14 $	imes$ 14 mm)                | One-time PROM                |

| $\mu$ PD78P4026GC-×××-3B9 Note | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Preprogramming one-time PROM |

| μPD78P4026KK-T                 | 80-pin ceramic WQFN (14 $	imes$ 14 mm)               | EPROM                        |

**Note** QTOP<sup>TM</sup> microcontroller. "QTOP microcontroller" is a general term for a single-chip microcontroller with on-chip one-time PROM, for which total support is provided by NEC programming service, from programming to marking, screening, and verification.

#### (2) Quality grades

| Part Number                    | Dealvage                                             | Quality Crada                               |

|--------------------------------|------------------------------------------------------|---------------------------------------------|

| Part Number                    | Package                                              | Quality Grade                               |

| μPD784020GC-3B9                | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Standard                                    |

| μPD784021GC-3B9                | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Standard                                    |

| μPD784021GK-BE9                | 80-pin plastic TQFP (fine pitch) (12 $\times$ 12 mm) | Standard                                    |

| μPD784025GC-×××-3B9            | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Standard                                    |

| μPD784026GC-×××-3B9            | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Standard                                    |

| μPD78P4026GC-3B9               | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Standard                                    |

| $\mu$ PD78P4026GC-xxx-3B9 Note | 80-pin plastic QFP (14 $	imes$ 14 mm)                | Standard                                    |

| μΡD78P4026KK-T                 | 80-pin ceramic WQFN (14 $\times$ 14 mm)              | Not applicable<br>(for function evaluation) |

**Note** QTOP microcontroller. "QTOP microcontroller" is a general term for a single-chip microcontroller with on-chip one-time PROM, for which total support is provided by NEC programming service from programming to marking, screening, and verification.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# Caution The EPROM version of the $\mu$ PD78P4026 does not have a level of reliability intended for volume production of customers' equipment, and should only be used for experimental or preproduction function evaluation.

Remark ××× indicates ROM code suffix.

#### 1.2.4 Outline of functions

| Item                                     | Produ            | uct Name                                                                                                       | μPD784020                                                                                                                                                                            | μPD78402                                                                     | 21 μPD784025                                                                                                                                                                                                                                             | μPD784026       | μPD78P4026        |  |  |

|------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|--|--|

| Number of basic instructions (mnemonics) |                  | 113                                                                                                            |                                                                                                                                                                                      |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| General-purpose registers                |                  | 8 bits $\times$ 16 registers $\times$ 8 banks or 16 bits $\times$ 8 registers $\times$ 8 banks (memory mapped) |                                                                                                                                                                                      |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| Minimum instruction execution time       |                  | 160 ns/320 ns                                                                                                  | 640 ns/1,2                                                                                                                                                                           | 80 ns (at 25 MHz                                                             | operation)                                                                                                                                                                                                                                               |                 |                   |  |  |

| On-chip memory capacity ROM              |                  | None                                                                                                           |                                                                                                                                                                                      | 48 KB<br>(Mask ROM                                                           | 64 KB                                                                                                                                                                                                                                                    | 64 KB<br>(PROM) |                   |  |  |

|                                          |                  | RAM                                                                                                            | 512 bytes 2,048 bytes                                                                                                                                                                |                                                                              | ,                                                                                                                                                                                                                                                        |                 | \ - /             |  |  |

| Memory space                             |                  |                                                                                                                | 1 MB total both program and data                                                                                                                                                     |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| I/O ports                                | Total            |                                                                                                                | 46                                                                                                                                                                                   |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

|                                          | Input            |                                                                                                                | 8                                                                                                                                                                                    |                                                                              | 8                                                                                                                                                                                                                                                        | 64              |                   |  |  |

|                                          | Input/output     |                                                                                                                | 34                                                                                                                                                                                   |                                                                              | 56                                                                                                                                                                                                                                                       |                 |                   |  |  |

|                                          | Output           |                                                                                                                | 4                                                                                                                                                                                    |                                                                              | 0                                                                                                                                                                                                                                                        |                 |                   |  |  |

| Pins with                                | Pins with pull-u | p resistors                                                                                                    | 32                                                                                                                                                                                   |                                                                              | 54                                                                                                                                                                                                                                                       |                 |                   |  |  |

| additional                               | LED direct drive | -                                                                                                              | 8                                                                                                                                                                                    |                                                                              | 24                                                                                                                                                                                                                                                       |                 |                   |  |  |

| functions <sup>Note</sup>                | Transistor direc |                                                                                                                | 8                                                                                                                                                                                    |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| Real-time output                         |                  |                                                                                                                | 4 bits $\times$ 2, or                                                                                                                                                                | 8 bits × 1                                                                   |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| Timer/counters                           |                  | Timer/counte<br>(16 bits)                                                                                      | r 0:                                                                                                                                                                                 |                                                                              | ner register × 1 Pulse output capability<br>mpare register × 2 • Toggle output<br>pture register × 1 • PWM/PPG output<br>• One-shot pulse output                                                                                                         |                 |                   |  |  |

|                                          |                  | (8/16 bits) Com<br>Capt                                                                                        |                                                                                                                                                                                      | Capture register                                                             | $\begin{array}{ll} \mbox{mer register} \times 1 & \mbox{Pulse output capability} \\ \mbox{ompare register} \times 1 & \mbox{• Real-time output: 4 bits} \times 2 \\ \mbox{apture register} \times 1 \\ \mbox{put/compare register} \times 1 \end{array}$ |                 |                   |  |  |

|                                          |                  | -                                                                                                              |                                                                                                                                                                                      | $r \times 1$ • Toggle o<br>ster $\times 1$ • PWM/PP                          | •                                                                                                                                                                                                                                                        |                 |                   |  |  |

|                                          |                  | Timer 3:<br>(8/16 bits)                                                                                        |                                                                                                                                                                                      | Timer register $\times$ 1<br>Compare register $\times$ 1                     |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| Watchdog timer                           |                  | 1 channel                                                                                                      |                                                                                                                                                                                      |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| PWM output fund                          | ction            |                                                                                                                | 12-bit resolution × 2 channels                                                                                                                                                       |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| Serial interfaces                        |                  |                                                                                                                | UART/IOE (3-wire serial I/O) : 2 channels (on-chip baud rate generator     CSI (3-wire serial I/O, SBI) : 1 channel                                                                  |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| A/D converter                            |                  |                                                                                                                | 8-bit resolution × 8 channels                                                                                                                                                        |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| D/A converter                            |                  |                                                                                                                | 8-bit resolution × 2 channels                                                                                                                                                        |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| Standby function                         |                  |                                                                                                                | HALT/STOP/                                                                                                                                                                           | IDLE mode                                                                    |                                                                                                                                                                                                                                                          |                 |                   |  |  |

| Interrupts                               | Hardware sour    | ces                                                                                                            | ,                                                                                                                                                                                    |                                                                              | : 7 (sampling clo                                                                                                                                                                                                                                        |                 | 1))               |  |  |

|                                          | Software source  | es                                                                                                             |                                                                                                                                                                                      |                                                                              | instruction, oper                                                                                                                                                                                                                                        | and error       |                   |  |  |

|                                          | Non-maskable     |                                                                                                                | Internal: 1, ex                                                                                                                                                                      |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

|                                          | Maskable         |                                                                                                                | Internal: 15, external: 6<br>• 4-level programmable priority                                                                                                                         |                                                                              |                                                                                                                                                                                                                                                          |                 |                   |  |  |

|                                          |                  |                                                                                                                | <ul> <li>3 kinds of process mode (vectored interrupt/macro service/conte</li> </ul>                                                                                                  |                                                                              |                                                                                                                                                                                                                                                          |                 | ontext switching) |  |  |

| Clock output fun                         | ction            |                                                                                                                | _                                                                                                                                                                                    | Selectable from fclk, fclk/2, fclk/4,<br>fclk/16 (also usable as 1-bit outpu |                                                                                                                                                                                                                                                          |                 |                   |  |  |

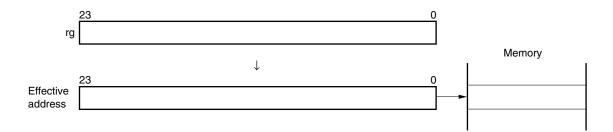

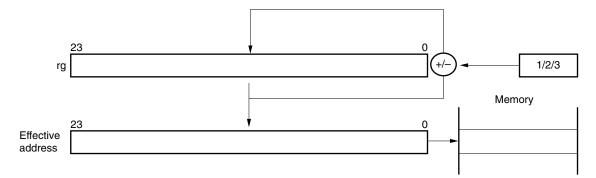

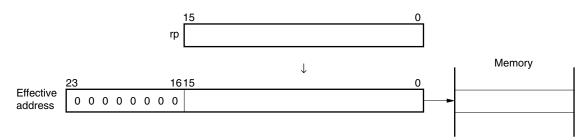

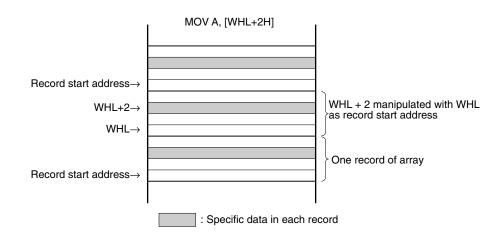

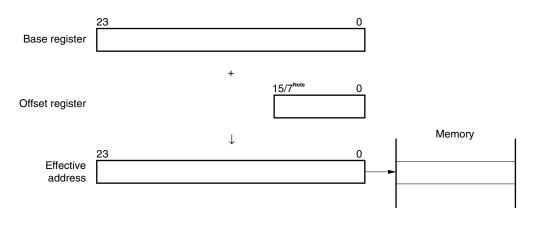

| Power supply vo                          | Itage            |                                                                                                                | VDD = 2.7 to \$                                                                                                                                                                      | 5.5 V                                                                        |                                                                                                                                                                                                                                                          |                 |                   |  |  |